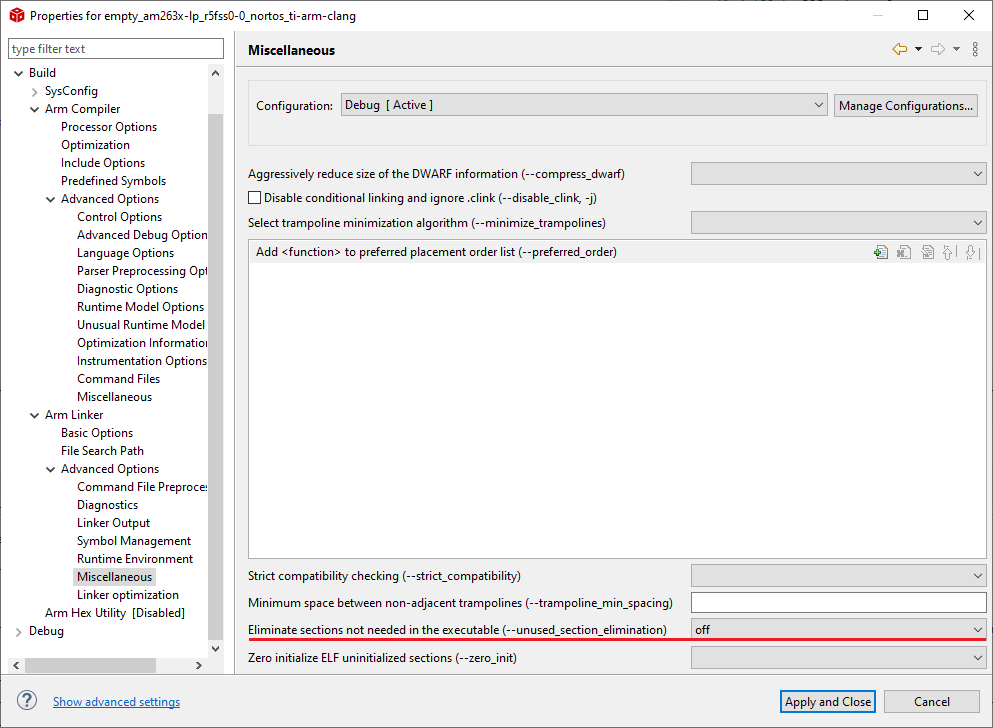

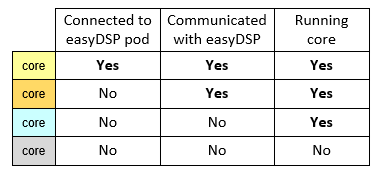

MCU cores are classified with 4

types in terms of easyDSP.

Yellow core : core that

easyDSP pod is connected to and easyDSP communicates with

Orange core : core that easyDSP pod is

not connected to but easyDSP communicates with

Blue core : core that easyDSP doesn't communicate

with

Gray core : core that doesn't run

AM263x has max 4 cores. Please choose core type

either yellow or orange core based on your application. Any core of AM263x

could be yellow or orange core.

Since blue and gray

core has no operation with easyDSP, no easyDSP related setting is required for

them.

Together with data cache usage, several cases are available as

below.

Case 1 :

It is the case that easyDSP monitors multi cores (core

a and b) and at least one of them uses data cache and IPC RPMessage is

usable for core to core communication.

easyDSP pod is connected to core

a via UART0, the variable of core a is accessed by core a.

To avoid cache

coherence issue, the variable (actually its memory location) of core b is

accessed by core b via core to core communication by IPC RPMessage. Please

refer to the arrow for data flow between easyDSP and cores.

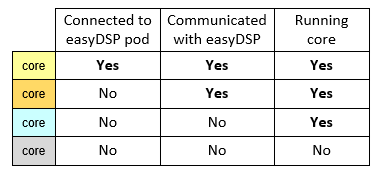

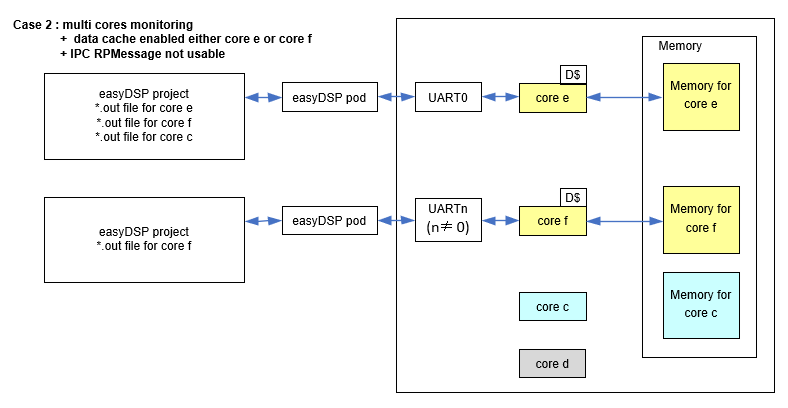

Case 2 :

In the case 1 but IPC RPMessage is not usable,

easyDSP pod should be connected to each core.

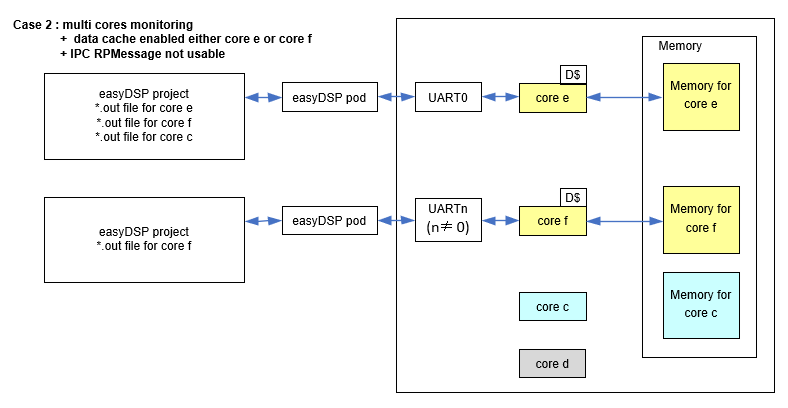

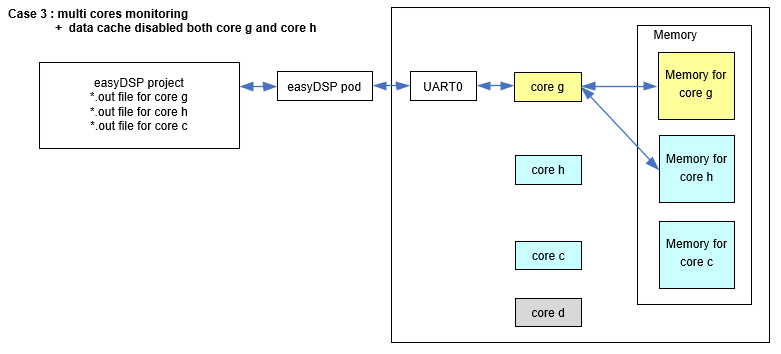

Case 3 :

It is the case that easyDSP monitors multi

cores and data cache is disabled in these cores.

All the

variables (and their memory location) are accessed by the core easyDSP

pod is connected to.

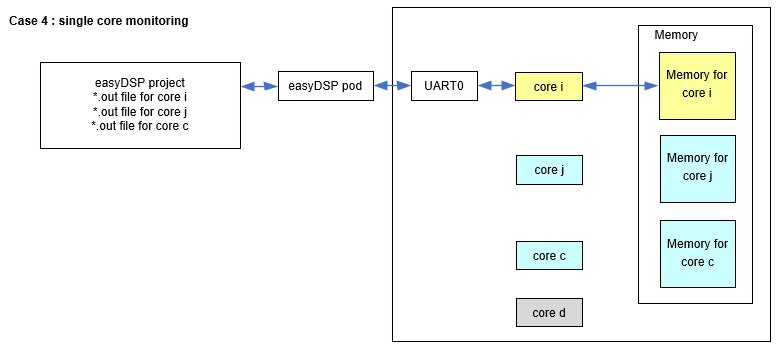

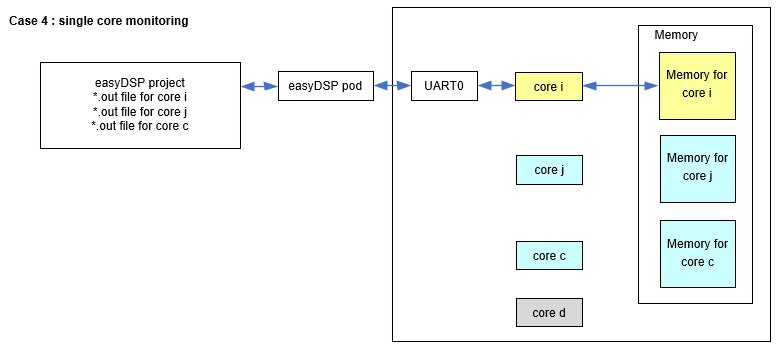

Case 4 :

It is the case that easyDSP monitors single core. In this case, we don't care whether the data cache is

enabled or not.

easyDSP uses the code

generated by SysConfig. Below figures are made based on SysConfig

1.13.0.

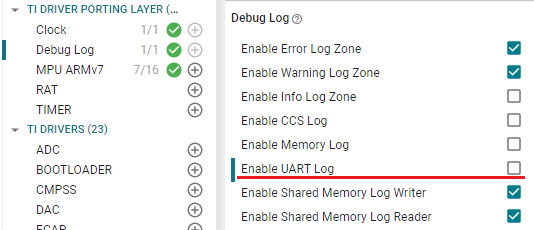

Since easyDSP communicates with MCU via UART0, please

disable 'Debug Log > Enable UART Log' or use another UART than UART0

for it.

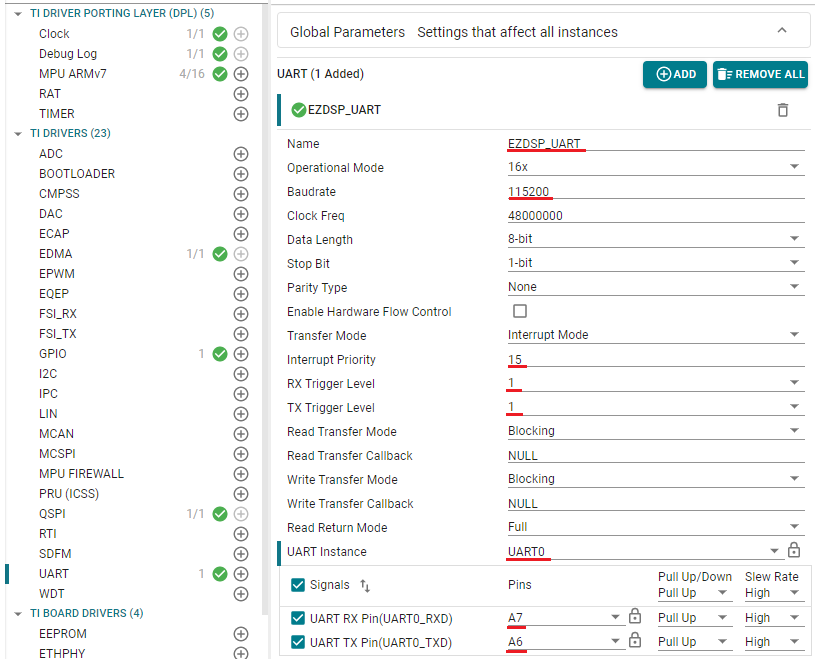

UART related setting is required for all the cores

easyDSP pod is connected to, that is, yellow cores.

The name of UART module should be 'EZDSP_UART'.

The baudrate is selectable but it should be same to that of easyDSP

project setting. The data format should be 8bit data, one stop bit and no parity

bit. The priority of UART interrupt should be as low as possible such as

15. TX and RX pins are that of UART0 MUXMODE 0. Exceptionally, UART of

core f in STEP1 could be other UART than UART0. Please check below for

details.

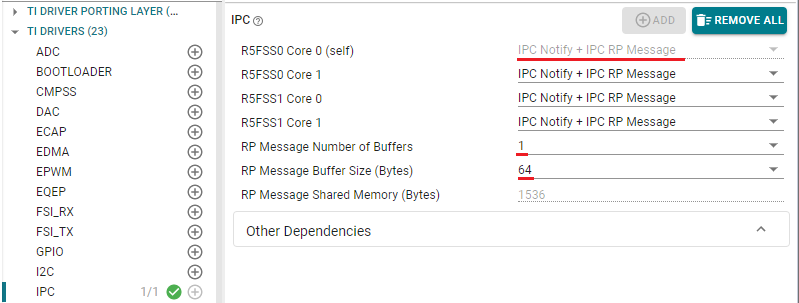

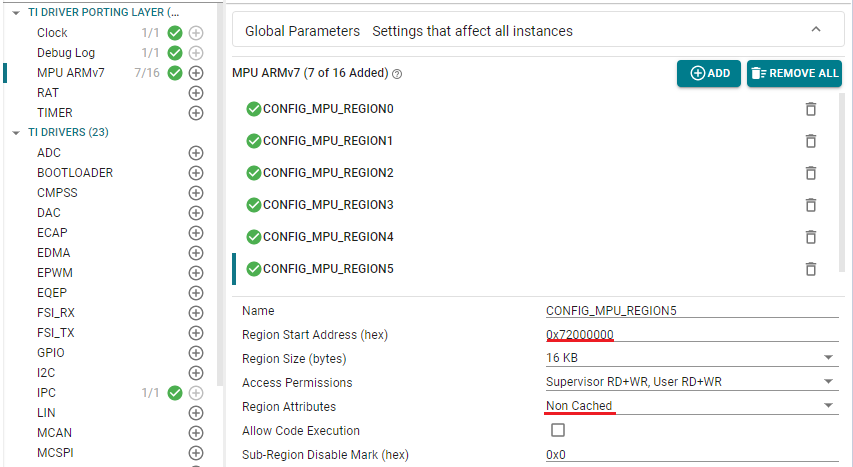

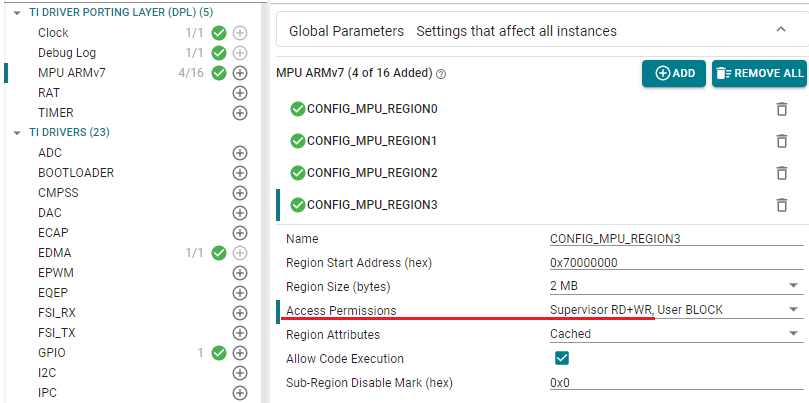

IPC setting is required for all the

cores using IPC RPMessage (core a and b in STEP1).

'IPC Notify + IPC

RP Message' should be used. And 'RP Message Number of Buffers' should be min.1

and 'RP Message Buffer Size' should be min 64. They are increased in case IPC

RPMessage is also used for other purpose than easyDSP. Also no cache should be

used for the shared buffer location (memory 16KB from

0x72000000).

'Supervion

RD+WR' is required for the memory area that easyDSP can access so that easyDSP reads/writes the

memory location.

According

to STEP1, easyDSP project should be generated to all the yellow cores, and user MCU project should

be modified for all the yellow and orange cores.

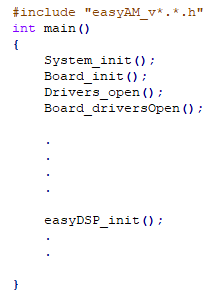

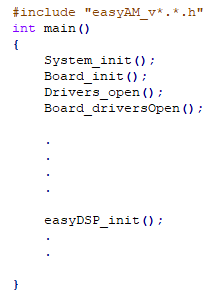

For the

yellow and orage cores, please include easyDSP header and source file

(easyAM_v*.*.h, easyAM_v*.*.c) into user MCU project. The suffix of file name will different by its

version. You can find these file in

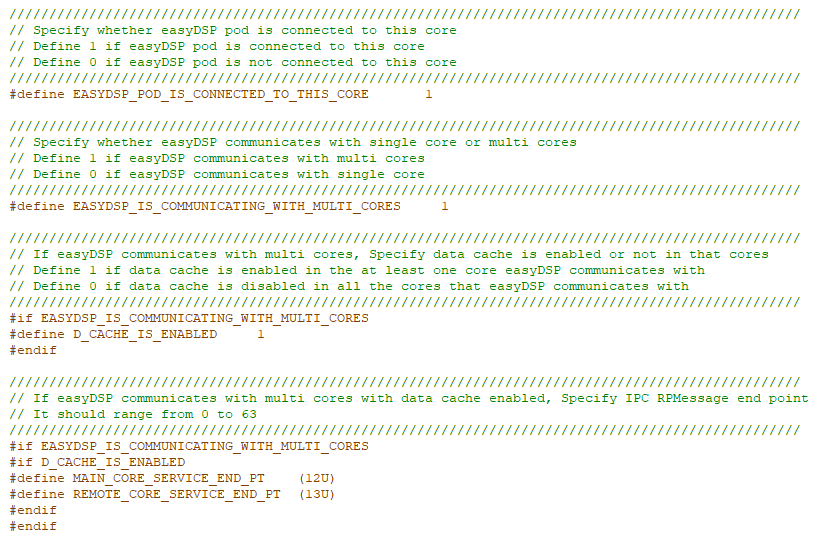

the folder easyDSP is installed (\source\AM2x). And set the #define directives based on your application.

And call easyDSP_init() function in the proper

location after some initialization functions.

Below is the detailed explanation by

cases.

Case 1

:

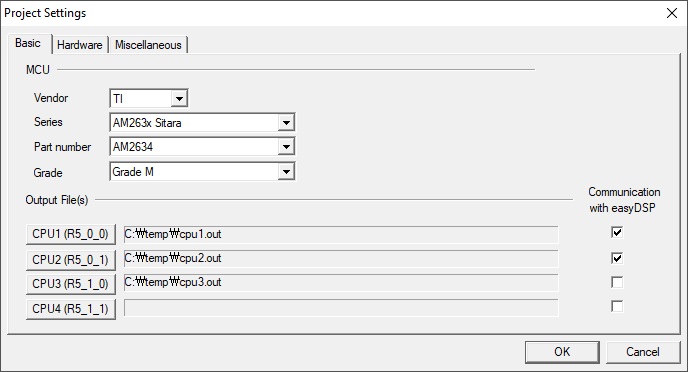

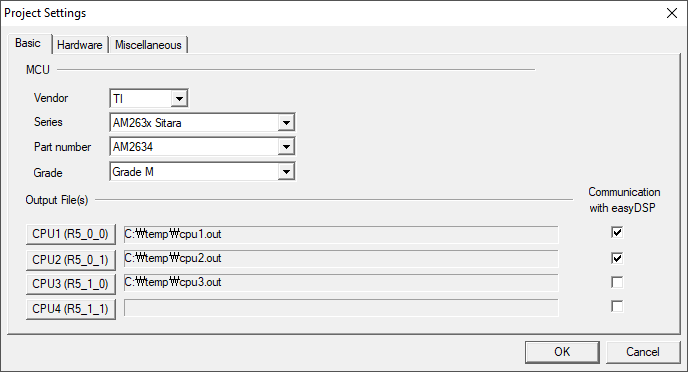

If core a, b, c and d are CPU1, 2, 3 and 4 respectively, the easyDSP project is

set as below.

The output files of

all the running cores are registered. And

CPU1 and CPU2 are checked as cores communicating with easyDSP.

The setting in the header file as below. Also two end

points (m and n) should be set for IPC RPMessage.

| Yellow core | Orange

core

|

|

setting in

easyAM.h | EASYDSP_POD_IS_CONNECTED_TO_THIS_CORE =1

EASYDSP_IS_COMMUNICATING_WITH_MULTI_CORES

=1

D_CACHE_IS_ENABLED =1

MAIN_CORE_SERVICE_END_PT = m

REMOTE_CORE_SERVICE_END_PT =

n

| EASYDSP_POD_IS_CONNECTED_TO_THIS_CORE = 0

EASYDSP_IS_COMMUNICATING_WITH_MULTI_CORES

=

1

D_CACHE_IS_ENABLED =

1

MAIN_CORE_SERVICE_END_PT = m

REMOTE_CORE_SERVICE_END_PT = n |

Case 2 :

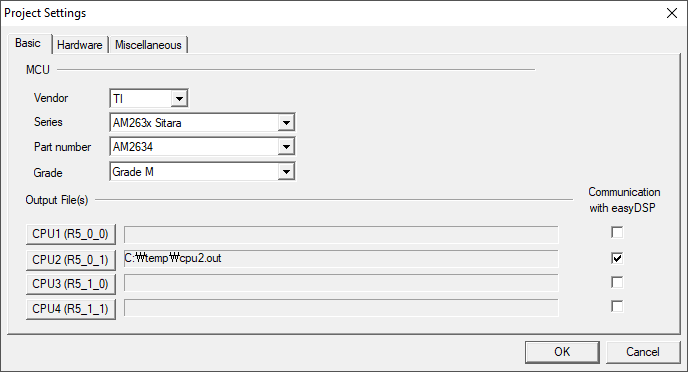

If core e, f, c and d are CPU1, 2, 3 and 4 respectively, the easyDSP project for core e

is set as below.

the easyDSP

project for core f is set as below.

To do RAM booting and flash programming, easyDSP pod should be connected to

the core via UART0.

Therefore register all the output files of running

cores to easyDSP project of core e (connected to easyDSP pod via UART0) so

that easyDSP project of core e can perform RAM booting and flash

programming.

On the other hand, don't perform RAM boooting and flash

programming in the easyDSP project of core f.

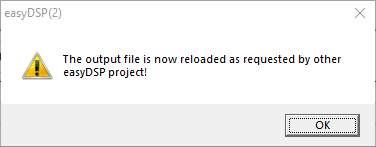

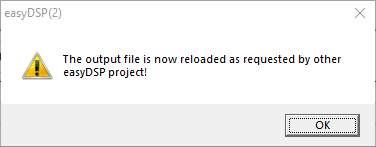

In case that user program of

core f is updated and downloaded to core f by easyDSP project of core e, the

easyDSP project of core f needs to reload its output file to update its

symbolic information.

This is done automatically if both easyDSP

projects (core e and core f) are running in the single PC. Then easyDSP

project of core f shows the message box below.

If both easyDSP projects run in the separate PC, then user need to do manually by executing the

menu 'MCU > Reload *.out' in the easyDSP project of core f.

The setting in

the header file as

below.

|

Yellow core

|

|

setting

in

easyAM.h |

EASYDSP_POD_IS_CONNECTED_TO_THIS_CORE =1

EASYDSP_IS_COMMUNICATING_WITH_MULTI_CORES = 0

|

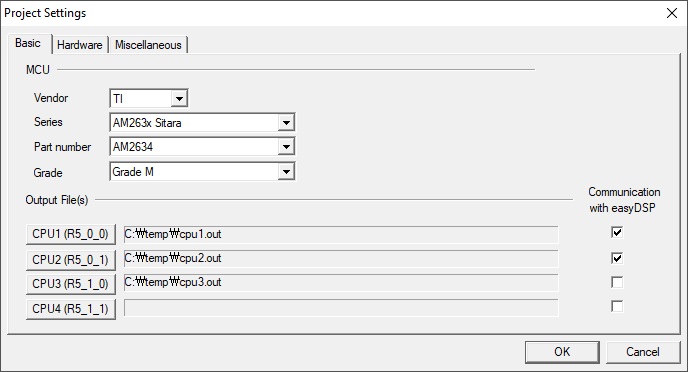

Case 3 :

If core g, h, c and d are CPU1, 2, 3 and 4

respectively, the easyDSP project for core g is set as below. The

output files of all the running cores are registered. And CPU1 and CPU2 are

checked as cores communicating with easyDSP.

The setting in the

header file as below.

|

Yellow core

|

|

setting in

easyAM.h

| EASYDSP_POD_IS_CONNECTED_TO_THIS_CORE =1

EASYDSP_IS_COMMUNICATING_WITH_MULTI_CORES

=1

D_CACHE_IS_ENABLED = 0 |

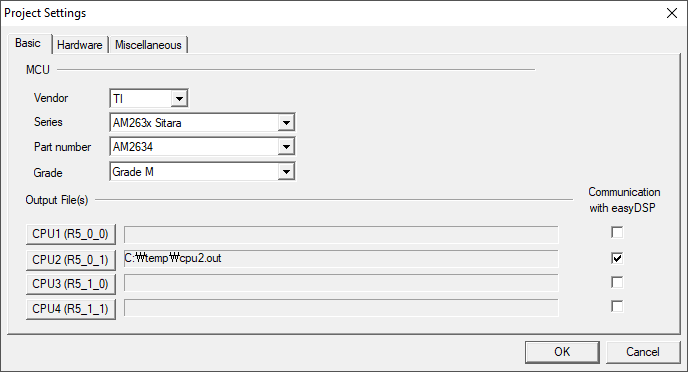

Case 4 :

If core i, j, c and d are CPU 1, 2, 3 and 4

respectively, the easyDSP project for core i is set as below. The

output files of all the running cores are registered. And CPU1 is

checked as core communicating with easyDSP.

The setting in the header file

as below.

|

Yellow core |

|

setting in

easyAM.h |

EASYDSP_POD_IS_CONNECTED_TO_THIS_CORE = 1

EASYDSP_IS_COMMUNICATING_WITH_MULTI_CORES

=0

|

1. Make sure that

rprc

file (*.rprc) is generated in every compilation with the

same name and in the same folder to the output file.

This is the default setting of TI

CCS.

rprc

file is

used for RAM booting and flash

programming.

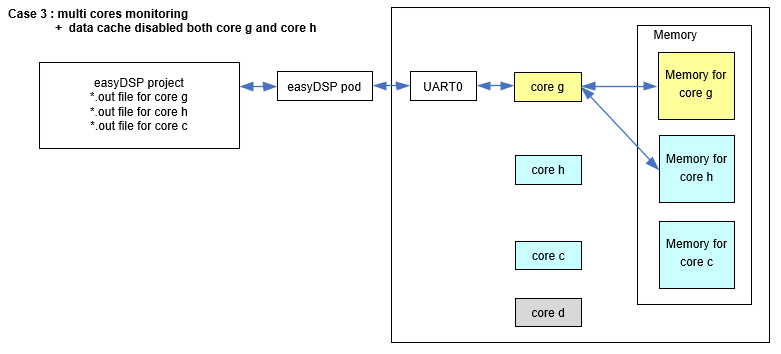

2. The debugging

information should be included in the output file. This is

the default setting of TI CCS. Otherwise, easyDSP can not recognize the variable.

3. The unused variables could be excluded from the

debug information depending on compiler's optimization level and linker

option. If necessary, you can set the linker option so that the unused

variables are not

excluded.