In

this page, factory default is assummed. If you change User OTP

(BOOTPIN_CONFIG, BOOTDEF), you should modify

the configuration accordingly.

MCU check below two pins at the reset to decide the

booting mode.

|

Boot Mode |

GPIO72 |

GPIO84 |

|

(Default boot mode

select pin 1) |

(Default boot mode

select pin 0)

|

|

Parallel IO

| 0 |

0 |

|

SCI / Wait Boot

|

0 |

1 |

|

CAN

|

1 |

0 |

|

Flash / USB

|

1 |

1 |

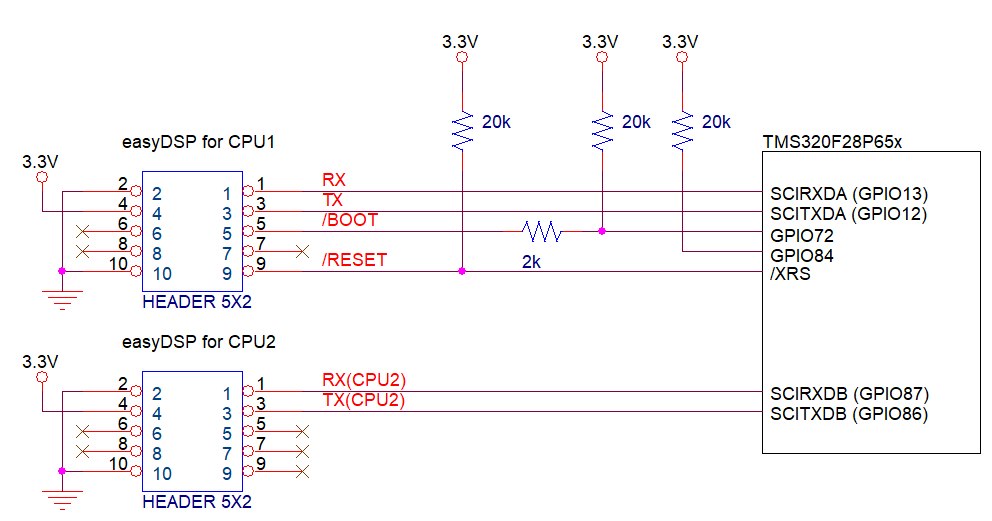

Since easyDSP uses two kinds boot modes, SCI boot mode (RAM

boot) and flash boot mode. Below connection is recommended between easyDSP

and MCU.

The

easyDSP connected to CPU1 should use SCI-A (GPIO13 and 12 fixed).

In case of dual cores MCU

(for example, F28P65xD), 2nd easyDSP is required to connect CPU2 via SCI-B. In

the easyDSP source file (easy28x_DriverLib.c or

easy28x_bitfield.c)

, GPIO 86 and 87 is used for

SCI-B. If another

GPIO port is required for SCI-B, please change the hardware connection and modify

the easyDSP source file (in the function of easyDSP_SCI_Init) accordingly by

yourself.

For other

considerations,

- power pin (#4) of

easyDSP 5x2 header should be connected to 3.3V

- TX/RX pins are

directly connected to

MCU pins

- In case

there is a reset IC between easyDSP /RESET and MCU /XRS, it should transfer

easyDSP /RESET signal to MCU /XRS within 0.5sec.

- In case you insert buffer IC between easyDSP

header and MCU, place buffer IC directly to easyDSP header so that all resistors

can be connected to directly MCU

- /RESET pin is connected to reset generation

circuit of MCU board (Time duration of /RESET pin

is around 500msec)

- In case you use pull-up resistor to

each pin, the value of pull-up resistor should be higher than a few kilo ohm

since there is 100Ω series resistor inside easyDSP pod

-

Please use appropriate

filter circuit to your reset generation circuit to prevent unintentional reset

generation.

- Refer to

here

for BOOT pin operation

mode.